Samsung intends to use GAA technology to extend its advantage and enhance the performance of its 1.4nm chips.

The components of the most sophisticated microprocessors available today are only a few nanometers in size, and very few businesses are able to make these chips. The market is dominated by Taiwan’s TSMC, with Samsung coming in a distant second. However, the runner-up might make some progress with its next significant chip advancement. According to preliminary information, Samsung’s planned 1.4nm production node will produce chips with significantly higher power and efficiency in the future.

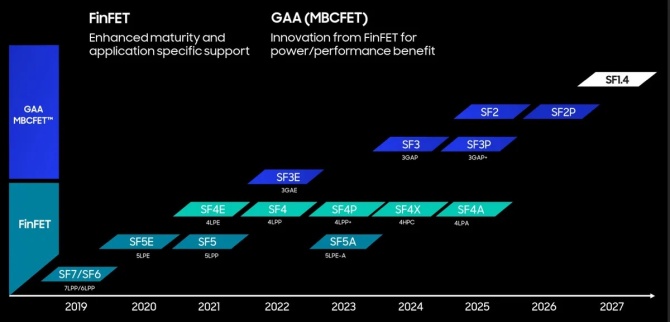

Vice president of Samsung Foundry Jeong Gi-Tae has provided a broad plan that would enable the business to catch up to TSMC. Currently, a number of chips may be manufactured using the 5nm (also known as SF5) process at Samsung’s foundry. It is also capable of producing 3nm and 4nm devices; however, it seems that Samsung is limited to using this technology for low-power embedded applications. Samsung plans to launch a comprehensive SF3 platform next year, providing clients with a range of options for 3nm processors. Still, it may take some time until we see a lot of 3nm Samsung chips. There are rumours that Google’s 2024 Tensor G4 will be built on Samsung’s 4nm (SF4) technology.

Samsung intends to upgrade its 3nm process to SF3P, a performance-tuned 3nm node, by the year 2025. Additionally, 2nm (SF2) chips will start to leave Samsung’s foundry at that time. The secret to raising transistor density, according to reports, is to use backside power delivery and enhanced gate-all-around (GAA) transistors in this generation of Samsung chips. Intel and TSMC intend to switch to GAA for their 2nm processes as well.

In 2027, Samsung’s GAA technology will prove invaluable in enabling the 1.4nm manufacturing node (SF1.4). These chips increase the number of GAA microsheets from three to four, which will result in smaller components. These devices will have faster processing and better current regulation because each transistor has more nanosheets. Additionally, the design will be more effective in preventing current leakage, which raises efficiency. The theoretical limit of silicon-based CPUs is being reached at 1.4nm. Each transistor at this size would only have three silicon atoms in width.

Because of Samsung’s packaging method, modern Samsung chips typically perform worse than comparable TSMC chips. Samsung is anticipated to introduce new bespoke packaging technology that will enable its clients to enhance the performance of their chips as it progresses towards finer production nodes. Samsung has made no secret of its desire to overtake TSMC, but it still has some work ahead of it.